自作PC@ふたば保管庫 [戻る]

|

速度が上がらないから |

|

>速度が上がらないから は?? |

|

非同期でスーパースカラーできるか? |

|

SoCなんかが非同期式ともいえるんじゃね? 複数のチップ間で非同期通信をしながら、不要な部分はクロック落として省電力とか |

|

非同期式論理回路は順序回路をゲート論理onlyに展開するが如し (実際にはメモリーに入れる手前でA+B=YのAかBの遅いほうを待つ、みたいな同期機構が残るが) 伝播遅延がクリティカルパスで押さえられるから神のごとき遅延配分で設計したら高速化の可能性はある が、現実にはちょっと… |

|

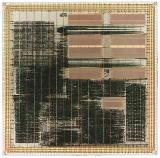

ていうかスレ画の如くチップ写真が構造色を発揮せず美しくないのが最大の難点 |

|

つねに最大限の速度で動いていて冷やせば冷やすほど速くなるんで、いちじき有望視されたことがあるんだけどね。 |

|

>冷やせば冷やすほど速くなるんで 道理で一般受けしなかったわけだ オーバークロッカーしか喜ばんね |

|

ソケ370時代にクロック違いのペン3でデュアルしてたけど あれは低い方に合わせられてたんだろうか |

|

>あれは低い方に合わせられてたんだろうか どうやって高い方に合わせるのか |

|

非同期式CPUの意味がわかってない人が混じってるな。 非同期式はクロック周波数に依存しないアーキティクチュア。 現行の同期式の場合、CPU全体にクロック信号を送っているので、実際には稼働していない部分にも無駄に電力を消費させている。 非同期式は、データが送られてきた部分のみ稼働させて、処理が終われば次のステップにデータを送ってやるだけなので、無駄な電力を削れる。 これは現行の同期式CPU内部の低速な部分に、常に足を引っ張られるというのを解決できることも意味する。 |

|

昨今のCPUだと使わない回路は電気供給遮断するので 大して変わらないかもです |

|

ディスクトップ クロックも変わるし部分的には非同期だったりもするし RISC/CISCのゲハじみた論争の頃と一緒でこの手のメリットは取り込めるものは取り込んでるんで看板で騒いでも意味ない |

|

歴史的意義を終えたからかな 現在の同期式CPUはモバイルからサーバまですべて ・暇してる回路は別演算で活用する ・それでも暇な回路は電源切る 低速バスに足引っ張られるのは非同期式も同様なので勝ち目はない |

|

非同期式は、常に100%のパフォーマンスで動作するから、 逆に無駄が多いんだよ。 |

|

>つねに最大限の速度で動いていて冷やせば冷やすほど速くなるんで、いちじき有望視されたことがあるんだけどね。 ジョセフソン素子?? |

|

haltしたら、動作自体が単純だから最高速でhaltするぜ! |

|

誰も書かないということは常識過ぎて面白みがないということか。 正解 デバッグが難しいから。同期式ロジックであれば、各クロックにおける状態が予想できる(つまり予想と違っていればその周辺にバグがいる)が、非同期式では全体的な検証が不可能(局部的には可能だが)。 |

|

電力が削れるってのはわかったけど データの流的にどうなの?たぶんそっちも踏まえてないとだめなんじゃね? |

|

>電力が削れるってのはわかったけど >データの流的にどうなの?たぶんそっちも踏まえてないとだめなんじゃね? 割り込み待ちとか、多大にクロックの掛かる処理に引っかかってる時でも、空いているモジュールは稼働できるんで、そのぶん処理は速くなる。 |